# High-precision Time-to-Digital-Converter

#### **PRODUCT DESCRIPTION**

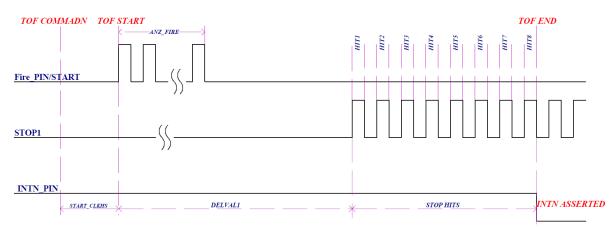

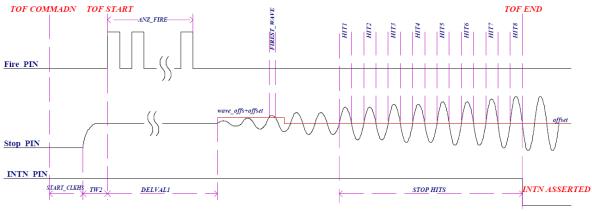

The MS1030 is a high-precision TDC circuit. It has the characteristics of high accuracy, high stability, and high efficiency. It has measurement accuracy of 15ps and a measurement range from 500ns to 4ms @ 4MHz. In the first wave mode, the offset range of the internal comparator is ±127mV, and a comparison bias voltage of - 128~124mV is also added; the measurement echo can be up to 8 echo pulses, built-in forward and reverse flow automatic measurement mode, and the value of 8 echo pulses and 8 echoes after the measurement is completed The sum of the wave pulses has independent result registers. This measurement mode not only improves the accuracy, but also greatly reduces the measurement power consumption.

### **FEATURES**

- Measurement Accuracy of 15ps

- Measurement Range from 500ns to 4ms @ 4MHz

- 8 echo signals can be measured

- Through the StartTOFRestart command and automatically measure forward and reverse flow

- High-precision Pulse Width Detection Unit

- Built-in Stable Low-drift Precision Comparator

- Built-in Programmable Comparator Bias Voltage, Programming Voltage -128~124mV

- Built-in First-wave Detection Function with Programmable Bias Voltage up to ±127mV

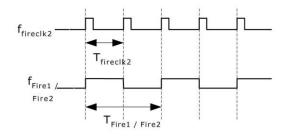

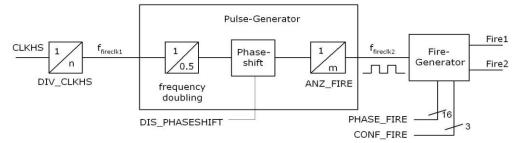

- Two pulse generators can generate 127 pulses

- Pulse generator sends pulse frequency: 62.5kHz~2MHz @ 4MHz

- Pulse generator single output 48mA current

- Two Pulse Output Pins with Reverse Function

#### **APPLICATIONS**

- Ultrasonic Water Meter

- Ultrasonic Heat Meter

- Ultrasonic Gas Meter

- Ultrasonic Flowmeter

- Ultrasonic Anemometer

#### **PRODUCT SPECIFICATION**

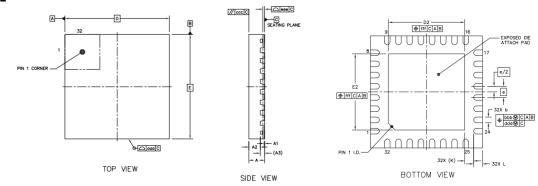

| Part Number | Package | Marking |

|-------------|---------|---------|

| MS1030      | QFN32   | MS1030  |

QFN32

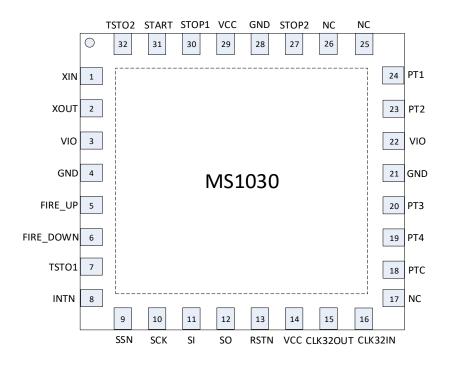

## **PIN CONFIGURATION**

# PIN DESCRIPTION

| Pin | Name      | I/O | Buffer Type  | Description                                | Unused |

|-----|-----------|-----|--------------|--------------------------------------------|--------|

| 1   | XIN       | Ι   |              | High-speed crystal Input                   | GND    |

| 2   | XOUT      | 0   |              | High-speed crystal Output                  |        |

| 3   | VIO       | -   |              | I/O Supply Voltage                         |        |

| 4   | GND       | -   |              | Ground                                     |        |

| 5   | FIRE_UP   | 0   | 48mA         | Fire Pulse Generator Output 1              |        |

| 6   | FIRE_DOWN | 0   | 48mA         | Fire Pulse Generator Output 2              |        |

| 7   | TSTO1     | 0   |              | Test Output Pin 1                          |        |

| 8   | INTN      | 0   | 4mA          | Interrupt Fag                              |        |

| 9   | SSN       | Ι   |              | Slave Select                               | GND    |

| 10  | SCK       | Ι   |              | Clock Serial Interface                     | GND    |

| 11  | SI        | Ι   |              | Data Input Serial Interface                | GND    |

| 12  | SO        | 0   | 4mA Tristate | Data Output Serial Interface               |        |

| 13  | RSTN      | Ι   |              | Reset Input, Low Active                    | VIO    |

| 14  | VCC       | -   |              | Core Supply Voltage                        |        |

| 15  | CLK32OUT  | 0   |              | Output 32kHz Clock Generator               |        |

| 16  | CLK32IN   | Ι   |              | Input 32kHz Clock Generator                | GND    |

| 17  | NC        | -   |              |                                            |        |

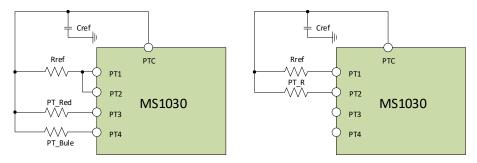

| 18  | PTC       | -   |              | Temperature Measurement Capacitor Terminal |        |

| 19  | PT4       | 0   | >96mA        | Port 4 Temperature Measurement             |        |

| 20  | PT3       | 0   | Open Drain   | Port 3 Temperature Measurement             |        |

| 21  | GND       | -   |              | Ground                                     |        |

| 22  | VIO       | -   |              | I/O Supply Voltage                         |        |

| 23  | PT2       | 0   | >96mA        | Port 2 Temperature Measurement             |        |

| 24  | PT1       | 0   | Open Drain   | Port 1 Temperature Measurement             |        |

| 25  | NC        | -   |              |                                            |        |

| 26  | NC        | -   |              |                                            |        |

| 27  | STOP2     | Ι   |              | Stop Input 2                               | GND    |

| 28  | GND       | -   |              | Ground                                     |        |

| 29  | VCC       | -   |              | Core Supply Voltage                        |        |

| 30  | STOP1     | Ι   |              | Stop Input 1                               | GND    |

| 31  | START     | Ι   |              | Start Input                                | GND    |

| 32  | TSTO2     | 0   |              | Test Output Pin 2                          |        |

Note: If the user does not use the above pins, please set the unused pins according to the connection in the

"Unused" column above.

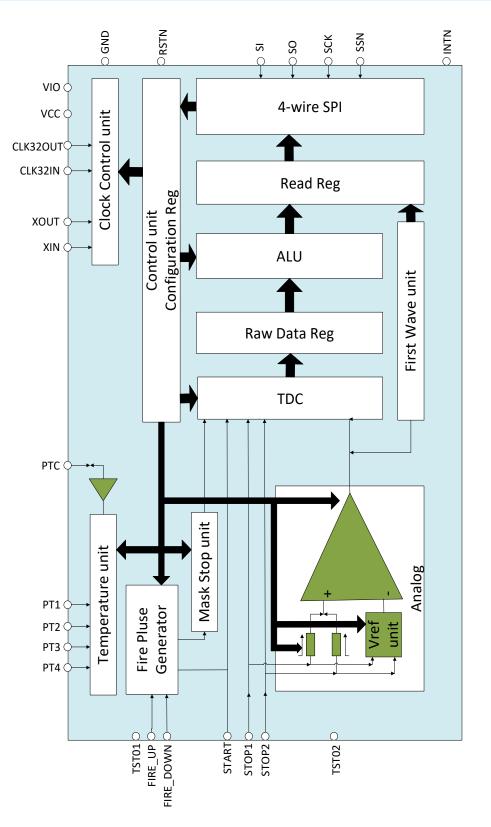

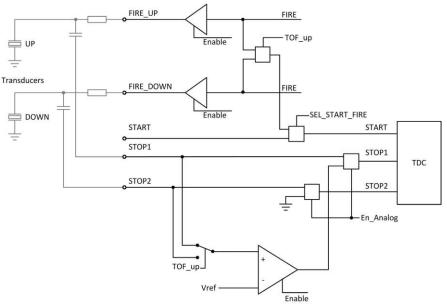

# **BLOCK DIAGRAM**

# ABSOLUTE MAXIMUM RATINGS

Any exceeding absolute maximum rating application causes permanent damage to device. Because long-time absolute operation state affects device reliability. Absolute ratings just conclude from a series of extreme tests. It doesn't represent chip can operate normally in these extreme conditions.

| Parameter            | Symbol | Range          | Unit |

|----------------------|--------|----------------|------|

| Core Supply Voltage  | Vcc    | -0.3 ~ 4       | v    |

| I/O Supply Voltage   | Vio    | -0.3 ~ 4       | v    |

| Input Voltage        | Vin    | -0.5 ~ Vcc+0.5 | v    |

| Storage Temperature  | Tstg   | -55 ~ 150      | °C   |

| Junction Temperature | Тј     | 125            | °C   |

| ESD Rating (HBM)     | ESD    | >4             | КV   |

# **RECOMMENDED OPERATING CONDITIONS**

| Parameter                    | Symbol  | Conditions               | Min | Тур | Max | Unit |

|------------------------------|---------|--------------------------|-----|-----|-----|------|

| Core Supply Voltage*         | Vcc     | Vcc= Vio                 | 2.5 |     | 3.6 | V    |

| I/O Supply Voltage           | Vio     |                          | 2.5 |     | 3.6 | V    |

| Normal Input Rising Time     | tri     |                          |     |     | 200 | ns   |

| Normal input falling time    | tfa     |                          |     |     | 200 | ns   |

| Schmitt Trigger Rising Time  | tri     |                          |     |     | 5   | ms   |

| Schmitt Trigger Falling Time | tfa     |                          |     |     | 5   | ms   |

| Ambient Temperature          | Та      | Tj must not exceed 125°C | -40 |     | 125 | °C   |

| Thermal Resistance           | Rth(j-) | Junction-ambient         |     | 28  |     | k/W  |

\*Including the oscillator pins XIN, XOUT, Clk32IN, Clk32OUT

# ELECTRICAL CHARACTERISTICS

# **DC Characteristics**

Vio = Vcc = 3V, Tj = -40  $\sim$  +85°C

| Parameter                          | Symbol | Conditions                                    | Min    | Тур   | Max    | Unit |

|------------------------------------|--------|-----------------------------------------------|--------|-------|--------|------|

| Current 32kHz                      | 132    | I <sub>CC</sub> +I <sub>IO</sub> , Only 32kHz |        | 4     |        | μA   |

|                                    | Ihs    | Vcc=Vio= 3.6V                                 |        | 200   |        | μA   |

| Current 4MHz                       |        | Vcc=Vio=3.0V                                  |        | 130   |        | μΑ   |

|                                    |        | Off                                           |        | <1    |        | μΑ   |

| Current Time Measuring Unit        | ltmu   | Only Time Measurement                         |        | 2     |        | mA   |

| Quiescent Current                  | Iddq   | All Clock Off, 85°C                           |        | <0.1  |        | μA   |

| Operating Current                  | lo     | TOF-UP/DOWN, 1/s,                             |        | 1.1   |        |      |

|                                    |        | PT1000,1/30s                                  |        | 0.15  |        | μA   |

| Current Time Measuring Unit        | ІТ     | Every 30 Seconds                              |        | 0.085 |        | μA   |

| Current of Analog Part             | lana   | Only Analog Part                              |        | 0.8   |        | mA   |

|                                    |        | Time is measured twice per second.            |        | 2.3   |        | μA   |

| Current of Complete Flow           | Itotal | Temperature is measured                       |        |       |        |      |

|                                    |        | every 30 seconds.                             |        |       |        |      |

| High Level Output Voltage          | Voh    | loh= tbd mA Vio=Min.                          | 0.8Vio |       |        | V    |

| Low Level Output Voltage           | Vol    | lol=tbd mA, Vio=Min                           |        |       | 0.2Vio | V    |

| High Level Input Voltage           | Vih    | LVTTL, Vio = Max.                             | 0.7Vio |       |        | V    |

| Low Level Input Voltage            | Vil    | LVTTL, Vio = Min.                             |        |       | 0.3Vio | V    |

| High Level Schmitt Trigger Voltage | Vth    |                                               | 0.7Vio |       |        | V    |

| Low Level Schmitt Trigger Voltage  | Vtl    |                                               |        |       | 0.3Vio | V    |

| Schmitt Trigger Hysteresis         | Vh     |                                               |        | 0.28  |        | V    |

### **Terminal Capacitance**

| Parameter      | Symbol | Conditions            | Min | Тур    | Max | Unit |

|----------------|--------|-----------------------|-----|--------|-----|------|

| Digital Input  | Cin    | Measured @ Vcc = Vio, |     | 7      |     |      |

| Digital Output | Со     | f = 1 MHz, T=25°C     |     |        |     | рF   |

| Bidirectional  | Cio    |                       |     | 9      |     |      |

| PT Ports       |        |                       |     | t.b.d. |     |      |

| Analog Input   |        |                       |     | t.b.d. |     |      |

# Analog Frontend

| Parameter                                                        | Symbol      | Conditions                                           | Min | Тур     | Max     | Unit |

|------------------------------------------------------------------|-------------|------------------------------------------------------|-----|---------|---------|------|

| Comparator Input Offset Voltage<br>(Chopper Stabilized)          |             |                                                      |     | 1       | 2       | mV   |

| Switch-on Resistance of Analog<br>Switches at STOP1/STOP2 Inputs | Rdson(AS)   |                                                      |     | 300     |         | Ohm  |

| Switch-on Resistance of<br>FIRE_UP,FIRE_DOWN Output Buffers      | Rdson(FIRE) | Symmetrical Outputs,<br>Rdson (HIGH)=<br>Rdson (LOW) |     | 4       |         | Ohm  |

| Output Current FIRE_UP,<br>FIRE_DOWN Output Buffers              | IFIRE       |                                                      |     | 48      |         | mA   |

| Analog Input Voltage                                             | Vana        |                                                      | 50  | 500     | VCCx2/3 | MVpp |

| STOP Bias Voltage                                                |             |                                                      |     | VCCx1/3 |         | V    |

| Comparator Transmission Delay                                    | Tpd         |                                                      |     |         | 100     | ns   |

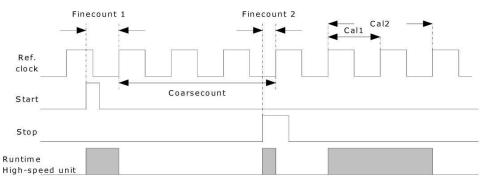

# Time Measuring Unit

Vio=Vcc=3.0V,Tj=25°C

| Parameter                  | Symbol | Conditions | Min    | Тур  | Max | Unit |

|----------------------------|--------|------------|--------|------|-----|------|

| Time Measurement Accuracy  | Тасс   | VCC=3.0V   |        | 15   |     | ps   |

| Measurement Resolution     | Tres   | VCC=3.0V   |        | 3.8  |     | ps   |

| Measuring Range*           | tm     | VCC=3.0V   | 0.0005 |      | 4   | ms   |

| Integral Non-linearity     | INL    | VCC=3.0V   |        | <0.1 |     | LSB  |

| Differential Non-linearity | DNL    | VCC=3.0V   |        | <0.1 |     | LSB  |

\*@4MHz

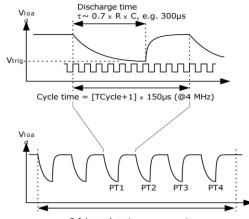

# **Temperature Measuring Unit\***

| Parameter                          |      | (      | Unit   |       |

|------------------------------------|------|--------|--------|-------|

| Sensor                             |      | PT500  | PT1000 |       |

| Resolution RMS                     |      | 17.5   | 17.5   | Bit   |

| SNR                                |      | 105    | 105    | dB    |

| Absolute Gain                      |      | 0.9912 | 0.9931 |       |

|                                    | 3.6V | 0.9923 | 0.9962 |       |

| Absolute Gain VS.Vio               | 3.0V | 0.9912 | 0.9960 |       |

|                                    | 2.5V | 0.9895 | 0.9956 |       |

| Gain Drift VS.Vio                  |      | 0.25   | 0.23   | %/V   |

| max. Gain Error@ d $^{\odot}$ =100 | 0k   | 0.05%  | 0.05%  |       |

| Gain-Drift VS. Temp                |      | 0.022  | 0.017  | %/10k |

| Gain-Drift VS. Vio                 |      |        |        | %/V   |

| Initial Zero Offset                |      | <20    | <10    | тК    |

| Offset Drift VS. Temp              |      | <0.05  | <0.03  | mK/°C |

| PSRR                               |      |        | >100   | dB    |

\* All values measured at Vio = Vcc = 3.0 V, Cload = 100 nF for PT1000 and 200 nF for PT500 (C0G-type).

# TIMING

At Vcc = 3.0V ±0.3V, ambient temperature -40°C to +85°C unless otherwise specified.

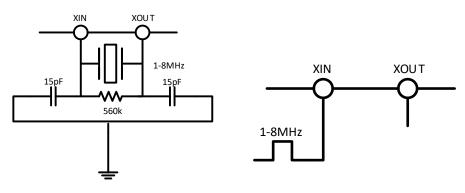

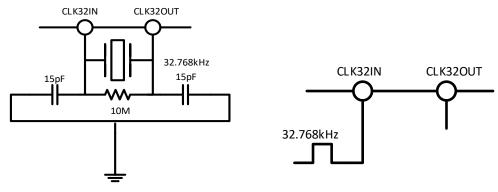

#### Oscillator

| Parameter                                        | Symbol | Min | Тур    | Max | Unit |

|--------------------------------------------------|--------|-----|--------|-----|------|

| 32kHz Reference Oscillator                       | Clk32  |     | 32.768 |     | kHz  |

| 32kHz Oscillator Start-up Time after Power-up    | t32st  |     | 3      |     | S    |

| High-speed Reference Oscillator                  | ClkHS  | 1   | 4      | 8   | MHz  |

| Oscillator Start-up Time with Ceramic Resonator  | toszst |     | 100    |     | μs   |

| Oscillator Start-up Time with Crystal Oscillator | toszst |     | 1      |     | ms   |

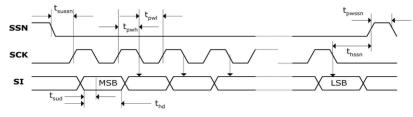

#### Serial Interface

| Parameter                              | Symbol             | Vio=2.5V | Vio=3.3V | Unit |

|----------------------------------------|--------------------|----------|----------|------|

| Serial Clock Frequency                 | f <sub>clk</sub>   | 15(Max)  | 20(Max)  | MHz  |

| Serial Clock, Pulse Width High         | $t_{pwh}$          | 30(Min)  | 25(Min)  | ns   |

| Serial Clock, Pulse Width Low          | t <sub>pwl</sub>   | 30(Min)  | 25(Min)  | ns   |

| SSN Enable to Valid Latch Clock        | t <sub>sussn</sub> | 40(Min)  | 10(Min)  | ns   |

| SSN Pulse Width between Write Cycles   | t <sub>pwssn</sub> | 50(Min)  | 40(Min)  | ns   |

| SSN Hold Time after SCLK Falling       | t <sub>hssn</sub>  | 40(Min)  | 25(Min)  | ns   |

| Data Set-up Time Prior to SCLK Falling | t <sub>sud</sub>   | 5(Min)   | 5(Min)   | ns   |

| Data Hold Time before SCLK Falling     | t <sub>hd</sub>    | 5(Min)   | 5(Min)   | ns   |

| Data Valid after SCLK Rising           | t <sub>vd</sub>    | 20(Min)  | 16(Min)  | ns   |

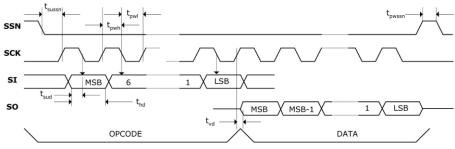

Serial Interface (SPI compatible, Clock Phase Bit =1, Clock Polarity Bit =0):

The serial interface is compatible with the 4-wire SPI. It requires a SerialSelectNot (SSN) signal, so it can't work in the 3-wire SPI interface.

The falling edge of the SSN or the rising edge of the first SCK would reset the state of INTN pin (interrupt pin) .

The transmission starts from the most significant bit (MSB) and ends with the least significant bit (LSB). The transfer is done in bytes. Data transfer can stop after each byte by sending a LOW-HIGH-LOW level to the SSN.

Figure1. SPI Write

Figure2. SPI Read

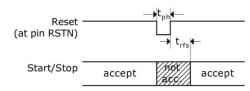

Figure3. Reset Timing

| Parameter                             | Symbol | Min | Max | Unit |

|---------------------------------------|--------|-----|-----|------|

| Reset Pulse Width                     | tph    | 30  | -   | ns   |

| Time after rising edge of reset pulse | trfs   | 30  | _   | ns   |

| before hits are accepted              | tits   | 30  | -   | 115  |

Note: After power-on reset it is necessary to wait minimum 500µs to settle the analog part.

### POWER SUPPLY

The MS1030 is a high-end mixed analog/digital device. To reach full performance of the chip, a good power supply is mandatory. It should be high capacitive and of low inductance.

The MS1030 provides two pairs of power supply terminals:

Vio - I/O supply voltage

Vcc - Core supply voltage

All ground pins should be connected to a ground plane on the printed circuit board. Vio and Vcc should be provided by a battery or fixed linear voltage regulator. Do not use switched regulators to avoid disturbances caused by the I/O supply.

The measurement quality of a time-to-digital converter depends on a good power supply. The chip sees mainly pulsed current and therefore a sufficient bypassing is mandatory:

Vcc 47  $\mu$ F (minimum 22  $\mu$ F)

Vio 100  $\mu F$  (minimum 22  $\mu F)$

The supply voltage should be provided through analog regulators. We strongly recommend not to use switch mode power supplies.

# **REGISTER DESCRIPTION**

## **OP CODE & Registers**

#### 1. OP Code

The operation code is used to read or write registers or execute operation commands.

The specific commands are as follows:

| Name                |      | Description                                                          |  |  |

|---------------------|------|----------------------------------------------------------------------|--|--|

| Name                | Code | Description                                                          |  |  |

| Write_REG0          | 0x80 | Write configuration register 0                                       |  |  |

| Write_REG1          | 0x81 | Write configuration register 1                                       |  |  |

| Write_REG2          | 0x82 | Write configuration register 2                                       |  |  |

| Write_REG3          | 0x83 | Write configuration register 3                                       |  |  |

| Write_REG4          | 0x84 | Write configuration register 4                                       |  |  |

| Read_TOF_UP_STOP1   | 0xb0 | Read the first STOP result register upstream                         |  |  |

| Read_TOF_UP_STOP2   | 0xb1 | Read the second STOP result register upstream                        |  |  |

| Read_TOF_UP_STOP3   | 0xb2 | Read the third STOP result register upstream                         |  |  |

| Read_TOF_UP_STOP4   | 0xb3 | Read the 4th STOP result register upstream                           |  |  |

| Read_TOF_UP_STOP5   | 0xb4 | Read the 5th STOP result register upstream                           |  |  |

| Read_TOF_UP_STOP6   | 0xb5 | Read the 6th STOP result register upstream                           |  |  |

| Read_TOF_UP_STOP7   | 0xb6 | Read the 7th STOP result register upstream                           |  |  |

| Read_TOF_UP_STOP8   | 0xb7 | Read the 8th STOP result register upstream                           |  |  |

| Read_TOF_UP_SUM     | 0xb8 | Read 8 STOP accumulation result registers upstream                   |  |  |

| Read_TOF_DN_STOP1   | 0xb9 | Read the first STOP result register downstream                       |  |  |

| Read_TOF_DN_STOP2   | 0xba | Read the second STOP result register downstream                      |  |  |

| Read_TOF_DN_STOP3   | 0xbb | Read the third STOP result register downstream                       |  |  |

| Read_TOF_DN_STOP4   | 0xbc | Read the 4th STOP result register downstream                         |  |  |

| Read_TOF_DN_STOP5   | 0xbd | Read the 5th STOP result register downstream                         |  |  |

| Read_TOF_DN_STOP6   | 0xbe | Read the 6th STOP result register downstream                         |  |  |

| Read_TOF_DN_STOP7   | 0xbf | Read the 7th STOP result register downstream                         |  |  |

| Read TOF DN STOP8   | 0xc0 | Read the 8th STOP result register downstream                         |  |  |

| Read_TOF_ DN_SUM    | 0xc1 | Read 8 STOP accumulation result registers downstream                 |  |  |

| Read_Temp_PT1       | 0xc2 | Read temperature measurement PT1 port result register                |  |  |

| Read_Temp_PT2       | 0xc3 | Read temperature measurement PT2 port result register                |  |  |

| Read_Temp_PT3       | 0xc4 | Read temperature measurement PT3 port result register                |  |  |

| Read_Temp_PT4       | 0xc5 | Read temperature measurement PT4 port result register                |  |  |

| Read PW First       | 0xd0 | Read the first wave pulse width result register                      |  |  |

| Read_PW_Stop1       | 0xd1 | Read the first STOP pulse width result register                      |  |  |

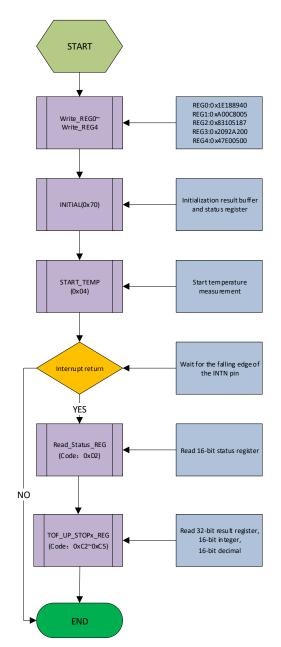

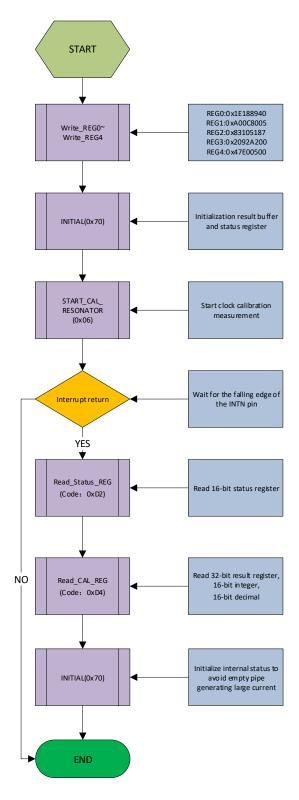

| Read_Status_REG     | 0xd2 | Read status register                                                 |  |  |

| Read_Comm_REG       | 0xd3 | Read communication detection register (lower 8 bits of register 0)   |  |  |

| Read_CAL_REG        | 0xd4 | Read clock calibration register                                      |  |  |

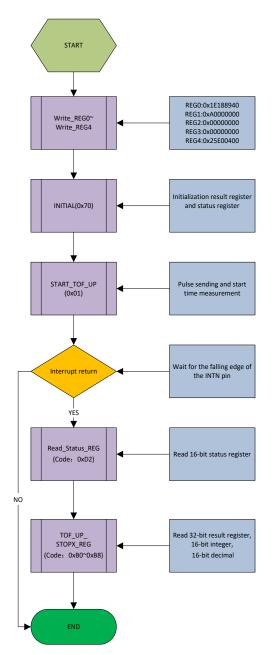

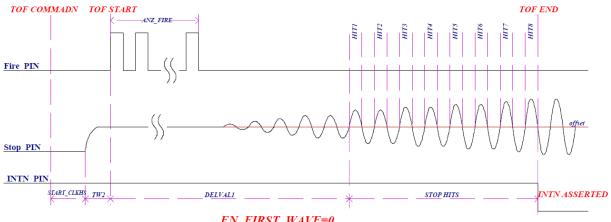

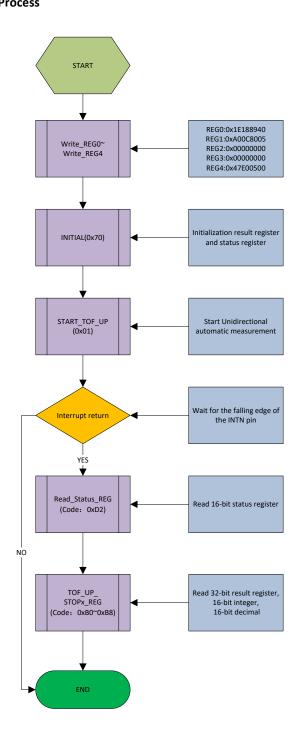

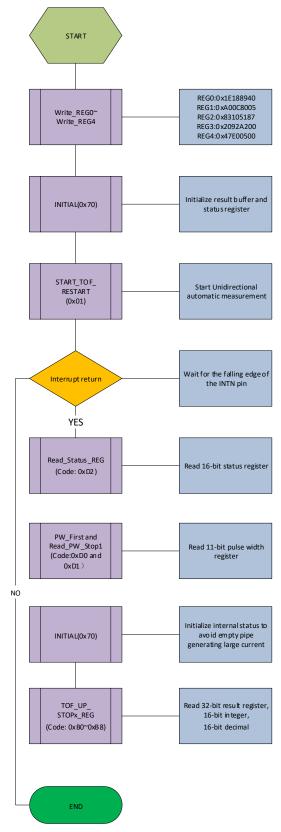

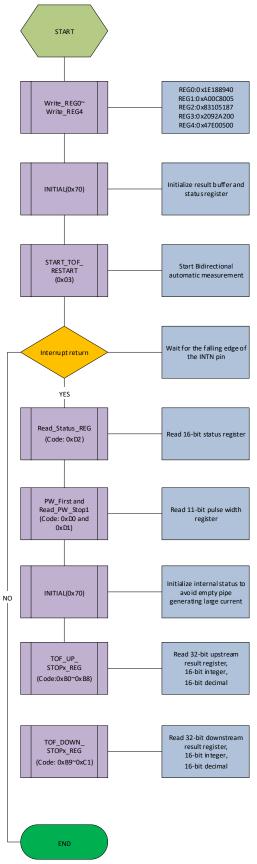

| INITIAL             | 0x70 | Initialization, only the result and status registers are initialized |  |  |

| POR                 | 0x50 | Software reset to initialize all registers                           |  |  |

|                     | 0,50 | Time measurement, sending pulse and receiving channel according      |  |  |

| START_TOF_UP        | 0x01 | to register configuration                                            |  |  |

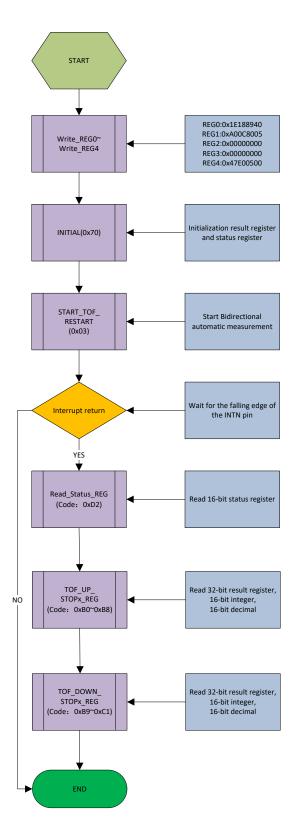

| START THE RESTART   | 0,02 | Bidirectional automatic measurement, automatic measurement           |  |  |

| START_TOF_RESTART   | 0x03 | and result storage                                                   |  |  |

| START_TEMP          | 0x04 | Temperature measurement                                              |  |  |

| START_TEMP_RESTART  | 0x05 | Two temperature measurements and two temperature tests               |  |  |

| START_CAL_RESONATOR | 0x06 | high-speed clock calibration tests                                   |  |  |

# 2. Registers

Registers store configuration parameters, measurement results, and detection status, and are executed by different operation codes. The specific register names and operation codes are as follows:

| Name Code Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                             |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|--|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Description                                                 |  |

| Write_REG0      0x80      Configuration register 0: 32 bits, write-only, not readable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                             |  |

| Write_REG1      0x81      Configuration register 1: 32 bits, write-only, not readable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Configuration register 1: 32 bits, write-only, not readable |  |

| Write_REG2      0x82      Configuration register 2: 32 bits, write-only, not readable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                             |  |

| Write_REG3      0x83      Configuration register 3: 32 bits, write-only, not readable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                             |  |

| Write_REG4      0x84      Configuration register 4: 32 bits, write-only, not readable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                             |  |

| TOF_UP_STOP1_REG      0xb0      Upstream 1st STOP result register: 16-bit integer, 16-bit decim                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | al                                                          |  |

| TOF_UP_STOP2_REG 0xb1 Upstream 2nd STOP result register: 16-bit integer, 16-bit decin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | nal                                                         |  |

| TOF_UP_STOP3_REG 0xb2 Upstream third STOP result register: 16-bit integer, 16-bit deci                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | mal                                                         |  |

| TOF_UP_STOP4_REG 0xb3 Upstream 4th STOP result register: 16-bit integer, 16-bit decim                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | al                                                          |  |

| TOF_UP_STOP5_REG 0xb4 Upstream 5th STOP result register: 16-bit integer, 16-bit decim                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | al                                                          |  |

| TOF_UP_STOP6_REG 0xb5 Upstream 6th STOP result register: 16-bit integer, 16-bit decim                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | al                                                          |  |

| TOF_UP_STOP7_REG 0xb6 Upstream 7th STOP result register: 16-bit integer, 16-bit decim                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | al                                                          |  |

| TOF_UP_STOP8_REG 0xb7 Upstream 8th STOP result register: 16-bit integer, 16-bit decim                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | al                                                          |  |

| Upstream 8 STOP accumulation result registers:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                             |  |

| TOF_UP_SUM_REG 0xb8 16-bit integer, 16-bit decimal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                             |  |

| TOF_DN_STOP1_REG      0xb9      Downstream 1st STOP result register: 16-bit integer, 16-bit dec                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | cimal                                                       |  |

| TOF_DN_STOP2_REG 0xba Downstream 2nd STOP result register: 16-bit integer, 16-bit de                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | cimal                                                       |  |

| TOF_DN_STOP3_REG 0xbb Downstream third STOP result register: 16-bit integer, 16-bit d                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ecimal                                                      |  |

| TOF_DN_STOP4_REG 0xbc Downstream 4th STOP result register: 16-bit integer, 16-bit dev                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | cimal                                                       |  |

| TOF_DN_STOP5_REG 0xbd Downstream 5th STOP result register: 16-bit integer, 16-bit de                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | cimal                                                       |  |

| TOF_DN_STOP6_REG 0xbe Downstream 6th STOP result register: 16-bit integer, 16-bit de                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | cimal                                                       |  |

| TOF_DN_STOP7_REG 0xbf Downstream 7th STOP result register: 16-bit integer, 16-bit de                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | cimal                                                       |  |

| TOF_DN_STOP8_REG 0xc0 Downstream 8th STOP result register: 16-bit integer, 16-bit dev                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | cimal                                                       |  |